EnSilica

| Private | |

| Industry | Semiconductor industry |

| Founded | 2001 |

| Headquarters | Wokingham, Berkshire, UK |

| Products | Microprocessor cores |

| Website | www.ensilica.com |

EnSilica is a design services and IP core company based in Wokingham, UK. It is known for its eSi-RISC configurable microprocessor cores for System-on-a-chip designs. In addition it is a recognized supplier of communications IP under the eSi-Comms family name.

History

EnSilica was formed in 2001 from a group of semiconductor professionals who had worked in engineering and management positions at a number of global telecommunications companies. Their knowledge of communications ASICs established the company as a leading provider of Design Services to UK high technology industry.

The company has grown at its Wokingham site and now includes a regional expert design center in Cambridge. The company regularly features in articles from Electronics Weekly, Cambridge Wireless, Silicon South West and the National Microelectronics Institute.

eSi-RISC

EnSilica develops soft processor IP for use in synthesized chip designs, specifically embedded systems under the family name eSi-RISC. EnSilica licenses its configurable processor core technology and provides three standard configurations eSi-1600, eSi-3200 and eSi-3250 as well as custom architectures.

The eSi-1600 16-bit CPU core is a low-cost, low-power processor ideal for integration into ASIC and/or FPGA designs. It offers similar performance to more expensive 32-bit CPUs while having a system cost comparable to that of 8-bit CPUs. Significant power savings are possible compared to 8-bit CPUs as applications require far fewer clock cycles to run.

The eSi-3200 32-bit CPU core is an extremely small, low-cost, low-power processor ideal for integration into ASIC and/or FPGA designs with on-chip memories. The eSi-3200 is particularly suited to embedded control applications.

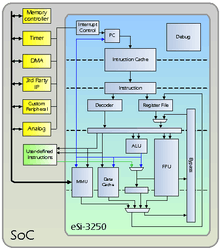

The eSi-3250 32-bit CPU is the top-of-the-range member in the eSi-RISC family of processor cores. It is targeted specifically for applications with high performance and large memory requirements.

For applications where high performance is required, the five-stage pipeline allows high clock frequencies to be achieved. While most instructions effectively execute in a single clock cycle, the deep pipeline allows the C and C++ compiler to schedule independent instructions such that instructions that can take multiple cycles to execute, appear to only take one clock cycle. Static branch prediction is employed to minimize the cost of branch instructions.

The eSi-RISC instruction set includes arithmetic and logical instructions (including barrel-shift, multiply and divide), comparisons, load and stores, branches and calls as well as system level instructions to control interrupts and enter lower power states. There are also a number of optional instructions and addressing modes that can be selected, should a specific application require them.

A number of instructions are reserved to allow the user to utilize user defined logic via a simple interface. This allows for otherwise unobtainable performance to be reached for many software inner loops. Instructions are encoded in either 16 or 32-bits, depending upon the size of the operands and the type of instruction. All of the commonly used instructions can be encoded in 16-bits. This ensures that high code density is achieved, while minimizing memory accesses to help conserve power.

The toolchain for eSi-RISC is based upon the industry standard GNU toolchain, which includes an optimizing C and C++ compiler, assembler, linker, debugger, simulator and binary utilities. All these tools can be driven by the customizable Eclipse IDE. The debugger can connect to the target CPU either via JTAG or a serial interface. Complete C and C++ libraries are supplied. The toolchain is available for both Windows and Linux hosts.

eSi-Comms

EnSilica license a range of communications IP specifically for modern COFDM communication systems. These include critical demodulation and Forward Error Correction modules such as Fast Fourier Transform, Viterbi Decoder and Reed Solomon Decoder. These IP cores can be used standalone or integrated into a SoC subsystem with the eSi-RISC processor.

External links

- Official website

- A GUIDE TO CPU CORES AND PROCESSOR IP. Focusing on CPU, DSP, and GPU. Third Edition. Kevin Krewell and J. Scott Gardner, April 2012. Section "EnSilica"