Ferroelectric RAM

| Computer memory types |

|---|

| Volatile |

| RAM |

| In development |

| Historical |

|

| Non-volatile |

| ROM |

| NVRAM |

| Early stage NVRAM |

| Mechanical |

| In development |

| Historical |

|

Ferroelectric RAM (FeRAM, F-RAM or FRAM) is a random-access memory similar in construction to DRAM but uses a ferroelectric layer instead of a dielectric layer to achieve non-volatility. FeRAM is one of a growing number of alternative non-volatile random-access memory technologies that offer the same functionality as flash memory.

FeRAM's advantages over flash include: lower power usage, faster write performance[1] and a much greater maximum read/write endurance (about 1010[2] to 1014[3] cycles). FeRAMs have data retention times of more than 10 years at +85°C (up to many decades at lower temperatures). Market disadvantages of FeRAM are much lower storage densities than flash devices, storage capacity limitations, and higher cost. FeRAM also has the unusual technical disadvantage of a destructive read process, necessitating a write-after-read architecture.

History

Ferroelectric RAM was proposed by MIT graduate student Dudley Allen Buck in his master's thesis, Ferroelectrics for Digital Information Storage and Switching, published in 1952.[4] In 1955 Bell Telephone Laboratories was experimenting with ferroelectric-crystal memories.[5] Development of FeRAM began in the late 1980s. Work was done in 1991 at NASA's Jet Propulsion Laboratory on improving methods of read out, including a novel method of non-destructive readout using pulses of UV radiation.[6] Much of the current FeRAM technology was developed by Ramtron, a fabless semiconductor company. One major licensee is Fujitsu, who operates what is probably the largest semiconductor foundry production line with FeRAM capability. Since 1999 they have been using this line to produce standalone FeRAMs, as well as specialized chips (e.g. chips for smart cards) with embedded FeRAMs. Fujitsu produced devices for Ramtron until 2010. Since 2010 Ramtron's fabricators have been TI (Texas Instruments) and IBM. Since at least 2001 Texas Instruments has collaborated with Ramtron to develop FeRAM test chips in a modified 130 nm process. In the fall of 2005, Ramtron reported that they were evaluating prototype samples of an 8-megabit FeRAM manufactured using Texas Instruments' FeRAM process. Fujitsu and Seiko-Epson were in 2005 collaborating in the development of a 180 nm FeRAM process. In 2012 Ramtron was acquired by Cypress Semiconductor.[7] FeRAM research projects have also been reported at Samsung, Matsushita, Oki, Toshiba, Infineon, Hynix, Symetrix, Cambridge University, University of Toronto, and the Interuniversity Microelectronics Centre (IMEC, Belgium).

Description

Conventional DRAM consists of a grid of small capacitors and their associated wiring and signaling transistors. Each storage element, a cell, consists of one capacitor and one transistor, a so-called "1T-1C" device. DRAM cells scale directly with the size of the semiconductor fabrication process being used to make it. For instance, on the 90 nm process used by most memory providers to make DDR2 DRAM, the cell size is 0.22 μm², which includes the capacitor, transistor, wiring, and some amount of "blank space" between the various parts — it appears 35% utilization is typical, leaving 65% of the space wasted.

DRAM data is stored as the presence or lack of an electrical charge in the capacitor, with the lack of charge in general representing "0". Writing is accomplished by activating the associated control transistor, draining the cell to write a "0", or sending current into it from a supply line if the new value should be "1". Reading is similar in nature; the transistor is again activated, draining the charge to a sense amplifier. If a pulse of charge is noticed in the amplifier, the cell held a charge and thus reads "1"; the lack of such a pulse indicates a "0". Note that this process is destructive, once the cell has been read. If it did hold a "1," it must be re-charged to that value again. Since a cell loses its charge after some time due to leak currents, it must be actively refreshed at intervals.

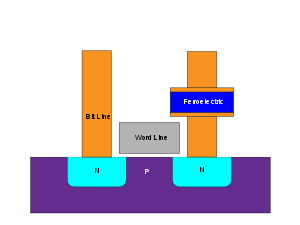

The 1T-1C storage cell design in an FeRAM is similar in construction to the storage cell in widely used DRAM in that both cell types include one capacitor and one access transistor. In a DRAM cell capacitor, a linear dielectric is used, whereas in an FeRAM cell capacitor the dielectric structure includes ferroelectric material, typically lead zirconate titanate (PZT).

A ferroelectric material has a nonlinear relationship between the applied electric field and the apparent stored charge. Specifically, the ferroelectric characteristic has the form of a hysteresis loop, which is very similar in shape to the hysteresis loop of ferromagnetic materials. The dielectric constant of a ferroelectric is typically much higher than that of a linear dielectric because of the effects of semi-permanent electric dipoles formed in the crystal structure of the ferroelectric material. When an external electric field is applied across a dielectric, the dipoles tend to align themselves with the field direction, produced by small shifts in the positions of atoms and shifts in the distributions of electronic charge in the crystal structure. After the charge is removed, the dipoles retain their polarization state. Binary "0"s and "1"s are stored as one of two possible electric polarizations in each data storage cell. For example, in the figure a "1" is encoded using the negative remnant polarization "-Pr", and a "0" is encoded using the positive remnant polarization "+Pr".

In terms of operation, FeRAM is similar to DRAM. Writing is accomplished by applying a field across the ferroelectric layer by charging the plates on either side of it, forcing the atoms inside into the "up" or "down" orientation (depending on the polarity of the charge), thereby storing a "1" or "0". Reading, however, is somewhat different than in DRAM. The transistor forces the cell into a particular state, say "0". If the cell already held a "0", nothing will happen in the output lines. If the cell held a "1", the re-orientation of the atoms in the film will cause a brief pulse of current in the output as they push electrons out of the metal on the "down" side. The presence of this pulse means the cell held a "1". Since this process overwrites the cell, reading FeRAM is a destructive process, and requires the cell to be re-written if it was changed.

In general, the operation of FeRAM is similar to ferrite core memory, one of the primary forms of computer memory in the 1960s. However, compared to core memory, FeRAM requires far less power to flip the state of the polarity and does so much faster.

Comparison with other memory types

Density

The main determinant of a memory system's cost is the density of the components used to make it up. Smaller components, and fewer of them, means that more cells can be packed onto a single chip, which in turn means more can be produced at once from a single silicon wafer. This improves yield, which is directly related to cost.

The lower limit to this scaling process is an important point of comparison. In general, the technology that scales to the smallest cell size will end up being the least expensive per bit. In terms of construction, FeRAM and DRAM are similar, and can in general be built on similar lines at similar sizes. In both cases, the lower limit seems to be defined by the amount of charge needed to trigger the sense amplifiers. For DRAM, this appears to be a problem at around 55 nm, at which point the charge stored in the capacitor is too small to be detected. It is not clear as to whether FeRAM can scale to the same size, as the charge density of the PZT layer may not be the same as the metal plates in a normal capacitor.

An additional limitation on size is that materials tend to stop being ferroelectric when they are too small.[8][9] (This effect is related to the ferroelectric's "depolarization field".) There is ongoing research on addressing the problem of stabilizing ferroelectric materials; one approach, for example, uses molecular adsorbates.[8]

To date, the commercial FeRAM devices have been produced at 350 nm and 130 nm. Early models required two FeRAM cells per bit, leading to very low densities, but this limitation has since been removed.

Power consumption

The key advantage to FeRAM over DRAM is what happens between the read and write cycles. In DRAM, the charge deposited on the metal plates leaks across the insulating layer and the control transistor, and disappears. In order for a DRAM to store data for anything other than a very short time, every cell must be periodically read and then re-written, a process known as refresh. Each cell must be refreshed many times every second (~65 ms[10]) and this requires a continuous supply of power.

In contrast, FeRAM only requires power when actually reading or writing a cell. The vast majority of power used in DRAM is used for refresh, so it seems reasonable to suggest that the benchmark quoted by TTR-MRAM researchers is useful here too, indicating power usage about 99% lower than DRAM. The destructive read aspect of FeRAM may put it at a disadvantage compared to MRAM, however.

Another non-volatile memory type is flash RAM, and like FeRAM it does not require a refresh process. Flash works by pushing electrons across a high-quality insulating barrier where they get "stuck" on one terminal of a transistor. This process requires high voltages, which are built up in a charge pump over time. This means that FeRAM could be expected to be lower power than flash, at least for writing, as the write power in FeRAM is only marginally higher than reading. For a "mostly-read" device the difference might be slight, but for devices with more balanced read and write the difference could be expected to be much higher.

Performance

DRAM performance is limited by the rate at which the charge stored in the cells can be drained (for reading) or stored (for writing). In general, this ends up being defined by the capability of the control transistors, the capacitance of the lines carrying power to the cells, and the heat that power generates.

FeRAM is based on the physical movement of atoms in response to an external field, which happens to be extremely fast, settling in about 1 ns. In theory, this means that FeRAM could be much faster than DRAM. However, since power has to flow into the cell for reading and writing, the electrical and switching delays would likely be similar to DRAM overall. It does seem reasonable to suggest that FeRAM would require less charge than DRAM, because DRAMs need to hold the charge, whereas FeRAM would have been written to before the charge would have drained. However, there is a delay in writing because the charge has to flow through the control transistor, which limits current somewhat.

In comparison to flash, the advantages are much more obvious. Whereas the read operation is likely to be similar in performance, the charge pump used for writing requires a considerable time to "build up" current, a process that FeRAM does not need. Flash memories commonly need a millisecond or more to complete a write, whereas current FeRAMs may complete a write in less than 150 ns.

On the other hand, FeRAM has its own reliability issues, including imprint and fatigue. Imprint is the preferential polarization state from previous writes to that state, and fatigue is increase of minimum writing voltage due to loss of polarization after extensive cycling.

The theoretical performance of FeRAM is not entirely clear. Existing 350 nm devices have read times on the order of 50–60 ns. Although slow compared to modern DRAMs, which can be found with times on the order of 2 ns, common 350 nm DRAMs operated with a read time of about 35 ns,[11] so FeRAM performance appears to be comparable given the same fabrication technology.

Overall

FeRAM remains a relatively small part of the overall semiconductor market. In 2005, worldwide semiconductor sales were US $235 billion (according to the Gartner Group), with the flash memory market accounting for US $18.6 billion (according to IC Insights). The 2005 annual sales of Ramtron, perhaps the largest FeRAM vendor, were reported to be US $32.7 million. The much larger sales of flash memory compared to the alternative NVRAMs support a much larger research and development effort. Flash memory is produced using semiconductor linewidths of 30 nm at Samsung (2007) while FeRAMs are produced in linewidths of 350 nm at Fujitsu and 130 nm at Texas Instruments (2007). Flash memory cells can store multiple bits per cell (currently 3 in the highest density NAND flash devices), and the number of bits per flash cell is projected to increase to 4 or even to 8 as a result of innovations in flash cell design. As a consequence, the areal bit densities of flash memory are much higher than those of FeRAM, and thus the cost per bit of flash memory is orders of magnitude lower than that of FeRAM.

The density of FeRAM arrays might be increased by improvements in FeRAM foundry process technology and cell structures, such as the development of vertical capacitor structures (in the same way as DRAM) to reduce the area of the cell footprint. However, reducing the cell size may cause the data signal to become too weak to be detectable. In 2005, Ramtron reported significant sales of its FeRAM products in a variety of sectors including (but not limited to) electricity meters,[12] automotive (e.g. black boxes, smart air bags), business machines (e.g. printers, RAID disk controllers), instrumentation, medical equipment, industrial microcontrollers, and radio frequency identification tags. The other emerging NVRAMs, such as MRAM, may seek to enter similar niche markets in competition with FeRAM.

Texas Instruments proved it to be possible to embed FeRAM cells using two additional masking steps during conventional CMOS semiconductor manufacture. Flash typically requires nine masks. This makes it possible for example, the integration of FeRAM on microcontrollers, where a simplified process would reduce costs. However, the materials used to make FeRAMs are not commonly used in CMOS integrated circuit manufacturing. Both the PZT ferroelectric layer and the noble metals used for electrodes raise CMOS process compatibility and contamination issues. Texas Instruments has incorporated an amount of FRAM memory into its MSP430 microcontrollers in its new FRAM series.[13]

See also

- Magnetic-core memory

- MRAM

- nvSRAM

- Phase-change memory

- Programmable metallization cell

- Memristor

- Racetrack memory

- Flash memory

- Ferroelectricity

- lead zirconate titanate

- Ramtron International

References

- ↑ http://www.inovacaotecnologica.com.br/noticias/noticia.php?artigo=fetram-memoria-nao-volatil&id=010110110929

- ↑ https://www.fujitsu.com/us/Images/MB85R4001A-DS501-00005-3v0-E.pdf

- ↑ http://www.cypress.com/file/136476/download

- ↑ Dudley A. Buck, "Ferroelectrics for Digital Information Storage and Switching." Report R-212, MIT, June 1952.

- ↑ Ridenour, Louis N. (June 1955). "Computer Memories". Scientific American Magazine: 92. Archived from the original on 2016-08-22. Retrieved 2016-08-22.

- ↑ Optically Addressed Ferroelectric Memory with Non-Destructive Read-Out

- ↑ http://www.bizjournals.com/denver/news/2012/11/21/cypress-semiconductor-completes.html

- 1 2 Ferroelectric Phase Transition in Individual Single-Crystalline BaTiO3 Nanowires. See also the associated press release.

- ↑ Junquera and Ghosez, Nature, 2003, DOI 10.1038/nature01501

- ↑ TN-47-16: Designing for High-Density DDR2 Memory

- ↑ IEEE Xplore—Login

- ↑ "User Manual: Single phase, single rate, Credit Meter". Ampy Automation Ltd.

The FRAM is guaranteed for a minimum of 10,000,000,000 write cycles.

- ↑ "FRAM – Ultra-Low-Power Embedded Memory". Texas Instruments.

External links

- FRAM(FeRAM) Application Community Sponsored by Ramtron[Language: Chinese]

- FRAM overview by Fujitsu

- FeRAM Tutorial by the Department of Electrical and Computer Engineering at the University of Toronto

- FRAM operation and technology tutorial

- IC Chips